### SHORT TERM CERTIFIED INTERNSHIP CUM WINTER TRAINING PROGRAMME ON

# MICROELECTRONICS TECHNOLOGY AND VLSI DESIGN

- <u>6 weeks</u>, Course starts from 2<sup>nd</sup>

January 2024

- 10.30 AM to 5.00 PM, Monday to Friday

#### Offered by:

IC DESIGN &

FABRICATION CENTRE

Department of

Electronics &

Telecommunication

Engineering

Jadavpur University,

Kolkata – 700032

Website: www.jaduniv.edu.in E-mail: juiccentre@gmail.com Phone: (033) 2457-2406 / 2414-6217 M: 9830157714, 9903402142

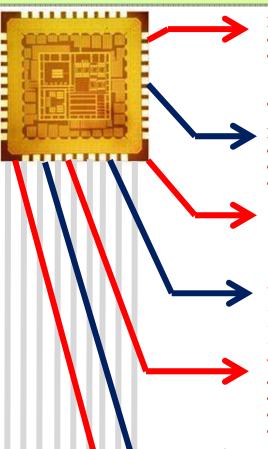

**Training Bus**

#### Fabrication and Characterization of semiconductor devices

- Mask Fabrication

- Hardware fabrication for all process of Microelectronics: cleaning, etching, oxidation, diffusion, photolithography and Metallization.

- Characterization of fabricated device.

#### FPGA based prototyping of Digital circuits

- Overview of CMOS logic gates

- Architectural design of digital circuits and logic synthesis

- FPGA-based prototyping

#### Nano-sensors: Technology and Application

- Smart nanomaterial for sensing applications

- Nano-sensor fabrication technologies

- Sensors with IoT.

#### **VLSI verification Process**

- Verification methodology and Verification process

- Reusable TB, Verification environment architecture

- Random coverage driven verification methodology

#### VLSI EDA tool handling

- Introduction to EDA Tools

- Netlist Using SPICE and layout design

- Programming using Verilog/VHDL

- Verification of design using waveform editor

#### **Analog MOS circuit**

- Single stage MOS amplifier

- Active loads, Current source, current sink, current mirror

- Single stage CMOS OpAmp

#### **Nanomaterial and Graphene**

- Understanding of synthesis and characterization

- Confinement effect

- Application of nonmaterial

- Graphene synthesis characterization and application

## **Laboratory Facilities**

## **Laboratory Handling**

- Programming using Verilog/VHDL

- Handling of different micro-fabrication techniques

- Fabrication of sensors

- Fabrication of Graphene material

Eligibility: The Candidate should be at least B.E./B.Tech  $2^{nd}$  Year and above in ECE / IEE / Electrical / CSE / IT/ M.sc Electronics Science or equivalent.

**Admission**: Application form will be issued from the IC Centre, Department of Electronics & Telecommunication Engineering, 3rd Floor, Jadavpur University, Kolkata or download from our website [www.jaduniv.edu.in or https://jadavpuruniversity.in]. Filled in application form shall be received at IC Centre during Monday to Friday, 11 AM to 5 PM.

**Course Fee:** Rupees **7,000/- (20% discount for JU students) + 18% GST** in demand draft should be drawn in favour of **"REGISTRAR, JADAVPUR UNIVERSITY"**, in any Nationalized branches of payable at Kolkata. Once deposited the course fee cannot be refunded. Hostel accommodation cannot be provided.

**Enclosure:** One copy of PP Size Photograph, Xerox copy of Madhyamik Admit Card / Birth Certificate, HS Mark sheet, Semesters Mark sheet [Attested / Self Attested copies of Mark sheets / Certificates to be enclosed]

# WHY THIS COURSE

# Know Your Indian Market :: Know Your Global Market

Government Tweaks Rs 76.000 Crore Semiconductor, Display Fab Scheme

To Woo Global Companies

The production linked incentive, or PLI, scheme announced in December last year had offered varying degree of fiscal support to different categories for development of semiconductors and display manufacturing ecosystem in India. These ranged from 30-50 per cent

**6** 0 0 0 0

# **HCLTech**

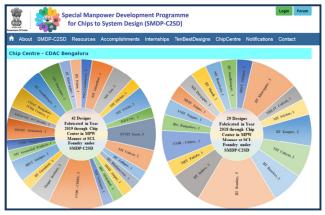

#### **Glimpse of IC Center outcomes:**

Nano crystalline

MEMS switched

Freq. synthesize chip and board level

Graphene set

Mask designed

Solar cell

Low noise amplifier

Micro heater

**Generate Startup**